Circuito Multiplexor Digital

|

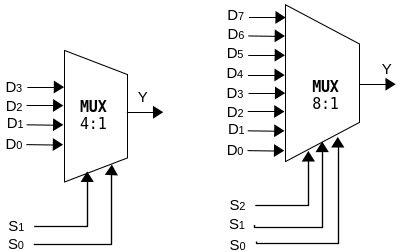

| Fig.1 Multiplexor Digital |

Bienvenido a este blog relacionado con la electrónica digital donde abordaremos en un principio, el diseño de circuitos lógicos combinatorios (CLC). Describiendo de manera breve y según el caso los siguientes aspectos:

- La teoría de funcionamiento

- La tabla de verdad

- Función lógica simplificada

- Esquema del circuito

- Descripción con HDL

- Implementacion

Veremos como realizar la descripción del circuito con el lenguaje Verilog, por lo que es recomendable que tengas conocimientos básicos sobre el uso de lenguajes de descripción de hardware HDL. Te dejo aquí un par de enlaces interesantes <Sitio1><Sitio2>. En vista que no realizaremos una implementación física como tal, vamos a verificar la funcionalidad lógica del circuito mediante simulación utilizando el software ModelSIM que viene instalado

con la suite Quartus/Intel que al día de hoy se llama QuestaSIM. Otra alternativa es utilizar EDA Playground que corre en linea desde un navegador, eso si necesitaras conexión en linea.

Aquí te dejo los enlaces para la descarga gratuita del software necesario previo registro:

Introducción

Un multiplexor (MUX) en su forma simple es un circuito que dispone de varias entradas y una sola salida, permitiendo establecer de manera selectiva cual de sus entradas se conecta con la salida. En la figura 2 podemos ver el diagrama de un multiplexor digital de dos canales y su operación.

| |

|

| |

|

Entonces es posible diseñar multiplexores de n-bit interconectando los multiplexores de 1-bit que ya vimos, por ejemplo en la figura 4 se ilustra un multiplexor de dos canales para datos de 4-bit.

|

| Fig4. Multiplexor de dos canales para datos de 4-bit |

Diseño Lógico del Circuito

Ahora veremos como funciona la lógica de un multiplexor, si vemos el ejemplo mas simple considerado en la figura 2, podemos determinar a partir de una tabla de verdad la siguiente función lógica

| Fig5. Análisis del Multiplexor de dos canales |

Un vez obtenida la función lógica podemos elaborar el esquema del circuito, utilizando la simbología de puertas lógicas estándar como puede ver en la siguiente figura.

|

| Fig6. Esquema del Circuito Multiplexor MUX2:1 |

Si consideramos ahora un multiplexor de cuatro canales como el que se observa en la figura 3 lado izquierdo, nuestro analisis en base a la tabla de verdad que ahora constara de seis entradas adra como resultado la siguiente función lógica.

|

| Fig7. Análisis del Multiplexor de cuatro canales |

|

| Fig8. Esquema del Circuito Multiplexor MUX4:1 |

Implementacion

Como les comente en esta sección no se realizara la implementación como tal, si no mas bien elaboraremos los módulos descriptivos del multiplexor y revisaremos su correcta operación lógica a través de diagramas de tiempo, para lo cual crearemos módulos de estimulo (testbench).

Tomaremos como ejemplo practico el multiplexor de cuatro canales que analizamos en la sección anterior, por lo que considerando el esquema del circuitos de la figura 8, es posible llevar a cabo la descripción estructural del circuito a nivel de puertas lógicas (Gate Level) utilizando las primitivas de verilog, resultando el siguiente código.

module mux4s(s0,s1,d0,d1,d2,d3,y);

input s0,s1; //Entradas para selección

input d0,d1,d2,d3;//Entradas D0 a D3

output y; //Salida

wire s0n, s1n; //Conexión para las lineas de control S

wire y1, y2, y3, y4;//Conexiones intermedias

not(s0n, s0); //linea negada de S0 (primitiva not)

not(s1n, s1); //linea negada de S1

and(y1, s1n,s0n, d0);//primitiva AND de tres entradas

and(y2, s1n, s0, d1);

and(y3, s1, s0n, d2);

and(y4, s1n, s0, d3);

or(y, y1, y2, y3, y4);//primitiva OR de cuatro entradas

endmodule

Si

consideramos el analisis de la figura 7, cuyo resultado es la función

lógica del circuito, podemos también realizar la descripción de esta

la función utilizando operadores de asignación con el siguiente

resultado.

module mux4s(s0,s1,d0,d1,d2,d3,y);

input s0,s1; //Entradas de selección

input d0,d1,d2,d3;//Entradas D0 a D3

output y; //Salida

wire y1, y2, y3, y4;//Conexiones intermedias

assign y1 = ~s1 & ~s0 & d0;//asigna el primer producto

assign y2 = ~s1 & s0 & d1;//asigna el segundo producto

assign y3 = s1 & ~s0 & d2;//asigna el tercer producto

assign y4 = s1 & s0 & d3;//asigna el cuarto producto

assign y = y1 | y2 | y3 | y4;//asigna en salida la suma total

endmodule

Un nivel mas abstracto en la que podemos prescindir del esquema de circuito y la función lógica, es la descripción a nivel del comportamiento (Behaviour Level) donde lo importante es conocer el funcionamiento del circuito, en este caso tomando como referencia el diagrama de bloques de la figura 3 nos bastare para elaborar el siguiente código.

module mux41s(s0,s1,d0,d1,d2,d3,y);

input s0,s1; //Entradas de selección

input d0,d1,d2,d3; //Entradas D0 a D3

output reg y; //Salida

always @(*) //Estructura que atiende cualquier cambio

case ({s1,s0}) //Se verifica la entrada S

2'b00: y = d0; //Primera asignación

2'b01: y = d1; //Segunda asignación

2'b10: y = d2; //Tercera asignación

2'b11: y = d3; //Cuarta asignación

endcase

endmodule

Si me preguntan cual de los tres modulo descriptivos elaborados conviene realizar, yo les diría que el ultimo por las siguientes dos razones:

- La abstracción que se logra describiendo el comportamiento nos ahorra bastante tiempo, porque realmente no necesitamos conocer la estructura de conexiones a nivel compuertas si ya sabemos que operaciones aritméticas o lógicas deben aplicarse para obtener el resultado esperado.

- Los dispositivos lógicos programables como las FPGA están construidos con miles o millones de Elementos Lógicos (LE) configurables, estas pequeñas unidades en realidad están formadas por una tabla de búsqueda LUT y Registros (Flip-Flop) con las que es posible definir su función durante un proceso conocido como síntesis, por lo tanto la optimización de un circuito en cuando a la cantidad de Elementos lógicos utilizados sera mejor con una descripción a nivel de registros, lo que se conoce como RTL (Register Transfer Level), esto a su vez garantiza que el código elaborado sea sintetizable en la FPGA.

Bueno para llevar a cabo las pruebas de funcionamiento escribiremos un modulo de estimulo para el circuito MUX4S, donde tomaremos como base de tiempo una milésima de segundo, para generaremos señales de pulso continuo a cada entrada del multiplexor con los siguientes valores: D0=1Hz, D1=2Hz, D2=4Hz y D3=8Hz, entonces la selección de cada canal se realizara en tiempos de un segundo (1000 ms). El código final se muestra a continuación.

`timescale 1ms/1ns

module mux4s_tb;

reg fq1, fq2, fq3, fq4;//Señales de entrada

reg sel0, sel1;//Lineas de entrada

wire fo; //Linea de salida

mux4s ins0(.s0(sel0),.s1(sel1),.d0(fq1),

.d1(fq2),.d2(fq3),.d3(fq4),.y(fo));

initial begin //Genera señal de 1Hz

while(1) #500 fq1 = !fq1; //500ms

end

initial begin //Genera señal de 2Hz

while(1) #250 fq2 = !fq2; //250ms

end

initial begin //Genera señal de 4Hz

while(1) #125 fq3 = !fq3;

end

initial begin //Genera señal de 8Hz

while(1) #62.5 fq4 = !fq4;

end

initial begin

#0000 fq1=0;fq2=0;fq3=0;fq4=0;

#0000 sel1=0;sel0=0; //Activa canal 1 segundo 0

#1000 sel1=0;sel0=1; //Activa canal 2 segundo 1

#1000 sel1=1;sel0=0; //Activa canal 3 segundo 2

#1000 sel1=1;sel0=1; //Activa canal 4 segundo 3

end

endmodule

Ahora se procede a correr la simulación del modulo con QuestaSIM dando como resultado el diagrama de tiempos que se observa en la figura 9, en la que se puede observar que el multiplexor MUX4S trabaja de forma correcta.

|

| Fig9. Diagrama de tiempos (simulación) |

Algo interesante de la descripción de nivel de comportamiento, es que es mas fácil ampliar la funcionalidad del circuito sobre la misma base del código, por ejemplo si nos planteamos llevar a cabo la descripción del circuito multiplexor que se ilustra en la figura 4, podría tomar como base el funcionamiento del multiplexor de dos canales y definir cada entrada como un dato de 4-bit, logrando el siguiente código.

module mux2s4b(s,a,b,y);

input s; //Entrada de selección

input [3:0] a,b; //Entradas de 4-bit

output reg [3:0] y; //Salida de 4-bit

always @(*) //Atiende cualquier cambio

case (s) //Verifica la entrada S

1'b0: y = a; //Primera asignación

1'b1: y = b; //Segunda asignación

endcase

endmodule

En mi canal de youtube dentro de la lista GOLAB1 resumo la implementación del multiplexor de dos canales para datos de 4-bit, donde la prueba de funcionamiento con una tarjeta FPGA, si quieres ver como se hizo la prueba aquí te dejo el enlace. <Click Aqui>

Conclusiones

Hemos visto de forma general como funciona un multiplexor digital, su diseño e implementación a través de Verilog, ya sea describiendo la estructura o el comportamiento el resultado obtenido mediante la simulación fue según lo esperado, por lo que resta continuar revisando mas ejemplos prácticos que nos permitan adquirir mas experiencia en el diseño de circuitos digitales.

Para finalizar solo quiero agradecer tu visita a mi blog, espero que el contenido de esta entrada hubiera sido de ayuda en tu formación educativa, favor cualquier consulta al respecto pueden escribirme a:

pablinzte@gmail.com / pablinza@me.com

@blinzar (Twitter)

Pablo Cesar Zárate.

No hay comentarios:

Publicar un comentario