Modulo Decodificador BCDTOSEG

|

Fig1. Muestra cuatro pantallas de 7 segmentos

|

Saludos cordiales, en

esta entrada, veremos el funcionamiento y diseño de un circuito decodificador de numero BCD a una pantalla de 7 segmentos, que son muy utilizados en diversas aplicaciones electrónicas, este trabajo complementa el avance académico para la materia de Sistemas Digitales, siendo importante que el lector ya cuente con conocimientos acerca de los circuitos combinatorios y uso del lenguaje de descripción Verilog.

Para elaborar el código del modulo y llevar a cabo pruebas de funcionamiento, utilizaremos uno de los siguientes programas:

Para implementar el circuito decodificador utilizaremos la tarjeta de ensayos basada en una FPGA GW1N-1 conocida como TangNANO.

Introducción a las Pantalla de 7 Segmentos

La pantalla o display de 7 segmentos, es un dispositivo opto-electrónico que nos permite visualizar un valor de 0 al 9 en su formato binario en una superficie distribuida por siete segmentos (diodos LED) que se activan individualmente para representar al numero decimal.

|

Fig2. Distribución de los segmentos para representar números

|

Existen dos tipos de pantallas de 7 segmentos que son: Ánodo Común y Cátodo Común, y se diferencian por la manera de como están conectados los LED's que conforman cada segmento, observe la siguiente figura.

|

Fig3. Conexión interna de los LED's

|

La configuración en Cátodo común requiere un voltaje positivo de +5V (1 logico) para activar los segmentos, mientras que en el modo Ánodo común se necesita 0V (0 logico) para la activación. Como cada segmento esta formado por uno o mas diodos LED que operan con una corriente de circulación nominal, es necesario utilizar resistencia limitadoras para no exceder la capacidad de corriente maxima y agotar la vida útil del dispositivo.

Una ventaja que aun mantiene el uso de estas pantallas de 7 segmentos es su bajo coste y fácil implementación, además de la variedad de presentaciones disponibles con dimensiones que van desde las 6 a 32 pulgadas y módulos que van de dos hasta ocho dígitos.

Diseño Lógico del Circuito

|

Fig4. Esquema del decodificador

|

Para describir el modulo de un decodificador BCD a 7 segmentos,

necesitaremos en primer lugar conocer los segmentos que se activaran en

la salida para cada cada numero presente en la entrada, siguiendo el principio de operación de un circuito combinatorio (CLC). La siguiente tabla de verdad nos muestra la relación de entrada y salida donde el numero decimal que se quiere mostrar ingresa en su forma binaria a través de las 4 entradas, siendo e3 el bit mas significativo y e0 el de menor peso, entonces la salida debe activar los segmentos correspondientes para forman el símbolo decimal.

|

Fig5. Decodificación para pantalla tipo CC

|

La tabla de verdad de la figura 6, muestra los valores de salida de cada numero binario considerando los dos tipos de pantalla: Cátodo Común y Ánodo Común.

|

Fig5. Tabla de salida para pantallas CC y AC

|

Ahora veremos como elaborar un modulo descriptivo Verilog para el comportamiento de este decodificador, al cual llamaremos bcdtoseg, asumiendo que se utilizara una pantalla del tipo cátodo común, utilizamos el editor del software de desarrollo citados previamente. El código final elaborado con sus respectivos comentarios es el siguiente:

module bcdtoseg(en, d0,d1,d2,d3,a,b,c,d,e,f,g);

input en; //Habilitador de salida

input d0,d1,d2,d3; //Entradas de numero binario

output a,b,c,d,e,f,g;//Salidas para los segmentos

wire [3:0] bcd; //Bus para los datos de entrada

reg [6:0] seg; //Registro para guardar valor de segmentos

assign bcd = {d3,d2,d1,d0}; //Asignación del numero binario al bus bcd

assign {g,f,e,d,c,b,a} = seg;//Asignación del registro seg a cada segmento

always @ (en, bcd) //Lista de eventos

if(en) //Solo si en esta activo

case(bcd) //Salida gfedcba segun numero bcd

4'b0000: seg = 7'b0111111; //numero 0

4'b0001: seg = 7'b0000110; //numero 1

4'b0010: seg = 7'b1011011; //numero 2

4'b0011: seg = 7'b1001111; //numero 3

4'b0100: seg = 7'b1100110; //numero 4

4'b0101: seg = 7'b1101101; //numero 5

4'b0110: seg = 7'b1111100; //numero 6

4'b0111: seg = 7'b0000111; //numero 7

4'b1000: seg = 7'b1111111; //numero 8

4'b1001: seg = 7'b1100111; //numero 9

default: seg = 7'b0000000;//Apaga todos los segmentos

endcase

endmodule

En caso de utilizar una pantalla del tipo AC, bastaría solo invertir la asignación del registro seg en cada segmento, esto seria así: assign {g,f,e,d,c,b,a} = ~seg;

Otra manera mas simplificada de describir este decodificador, seria utilizar directamente una bus de entrada para el numero y un bus de salida para los segmentos, tal como ser observa en el siguiente esquema.

|

Fig6. Decodificador con bus e/s

|

Entonces considerando el uso de un bus para la entrada y salida, los cambios a nuestro modulo descriptivo quedaran de la siguiente manera.

module bcdtoseg(en, bcd, seg);

input en; //Habilitador de salida

input [3:0] bcd; //Bus de entrada para el numero binario

output reg [6:0] seg;//Bus de salida para registro de segmentos

always @ (en, bcd) //Lista de eventos

if(en) //Solo si en esta activo

case(bcd) //Salida gfedcba según numero bcd

4'b0000: seg = 7'b0111111; //numero 0

4'b0001: seg = 7'b0000110; //numero 1

4'b0010: seg = 7'b1011011; //numero 2

4'b0011: seg = 7'b1001111; //numero 3

4'b0100: seg = 7'b1100110; //numero 4

4'b0101: seg = 7'b1101101; //numero 5

4'b0110: seg = 7'b1111100; //numero 6

4'b0111: seg = 7'b0000111; //numero 7

4'b1000: seg = 7'b1111111; //numero 8

4'b1001: seg = 7'b1100111; //numero 9

default: seg = 7'b0000000;//Apaga todos los segmentos

endcase

endmodule

Para ensayar el funcionamiento de nuestro decodificador, crearemos un modulo de estimulo con la que llevaremos a cabo una simulación. Este modulo llamara mediante una instancia al modulo bcdtoseg, para simplificar un poco consideraremos el decodificador que utiliza un bus para entrada y salida.

El modulo de estimulo tendrá la siguiente codificación:

module bcdtoseg_tb; //Nombre del modulo de estimulo

reg en; //Registro para estimular la entrada EN

reg [3:0] bcd; //Registro para estimular entrada bcd

wire [6:0] seg; //Bus de salida que muestra los segmentos

bcdtoseg ins0(en,bcd,seg); //crea instancia del modulo bcdtoseg

initial begin

#5 en=1;bcd=0; //Habilita e inicia el numero bcd a 0

#5 bcd=1; //numero bcd a 1

#5 bcd=2; //numero bcd a 2

#5 bcd=3;

#5 bcd=4;

#5 bcd=5;

#5 bcd=6;

#5 bcd=7;

#5 bcd=8;

#5 bcd=9; //numero bcd a 9

end

endmodule

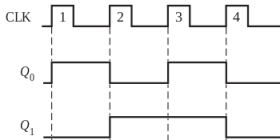

Para efectuar la simulación, utilizare el software ModelSim, donde posterior a la compilación de ambos módulos bcdtoseg y bcdtoseg_tb, se procede a iniciar la simulación adicionando las entradas y salidas que se representaran en un diagrama de tiempo, que nos mostrara el siguiente resultado.

|

Fig7. Diagrama de tiempos para simulación del decodificador

|

Este resultado no muestra que el decodificador funciona correctamente, y por lo tanto estará listo para su implementación.

Implementacion del circuito

Ahora como paso final veremos como implementar el decodificador que hemos creado en una FPGA, en mi caso utilizare la placa TangNANO y el software de diseño Gowin EDA, opcionalmente aquí te dejo un pequeño enlace introductorio que nos muestra como crear e implementar un proyecto con esta FPGA.

<<Introducción a FPGA TangNANO>>

Esta es la lista de los elementos utilizados:

- Placa FPGA TangNANO y cable USB-C

- Un HS-3191B, pantalla 7 segmentos tipo AC de 0.39 pulgadas.

- Una resistencia limitadora, lo recomendable es una por segmento.

- Cuatro pulsadores para establecer los valores en la entrada

- Protoboard y cables de conexión.

Con referencia a la hoja de datos de la placa TangNANO y la pantalla HS-3191B llevo a cabo las siguientes conexiones:

|

Fig8. Esquema de conexión al FPGA

|

Debemos tomar en cuenta lo siguiente; los pulsadores requieren la activación de las PULL-DOWN para establecer nivel logico verdadero, así mismo el modulo decodificador deberá ajustarse para una pantalla del tipo Ánodo Común. |

Fig9. Circuito decodificador en TangNANO

|

Como resumen de todo lo descrito en la sección, dejo un vídeo donde se observa la creación e implementación del proyecto con el software GoWin EDA.

Haz click <<aquí>> para descargar la carpeta del proyecto Para

finalizar solo quiero agradecer tu visita a mi blog, espero que el

contenido de esta entrada hubiera sido de ayuda en tu formación

educativa, favor cualquier consulta al respecto pueden escribirme a:

pablinzte@gmail.com / pablinza@me.com

Pablo Cesar Zárate.